## INTRODUCTION

Hewlett-Packard's line of seven segment LED display products can be divided into two broad categories. The first product family is the large seven segment display which is constructed using individual LEDs for each segment. These large single digit LED display devices have become common in instruments throughout the industry. The other standard type of seven segment device is known as the monolithic display. Monolithic displays are constructed by diffusing several LED junctions in a single GaAsP die. This type of display is characterized by its small size, low cost, and low power requirements. The monolithic display typically has several digits per package and is often found in calculators and hand held or portable instruments.

This application note begins with a detailed explanation of the two basic product lines that Hewlett-Packard offers in the seven segment display market. This discussion includes mechanical construction techniques, character heights, and typical areas of application. The two major display drive techniques, dc and strobed, are covered. The resultant tradeoffs of cost, power, and ease of use are discussed. This is followed by several typical instrument applications including counters, digital voltmeters, and microprocessor interface applications. Several different microprocessor based drive techniques are presented incorporating both the monolithic and the large seven segment LED displays.

The application note contains a discussion of intensity and color considerations made necessary if the devices are to be end stacked. Hewlett-Packard has made several advances in the area of sunlight viewability of LED displays. The basic theory is discussed and recommendations made for achieving viewability in direct sunlight. Information concerning display mounting, soldering, and cleaning is presented. Finally, an extensive set of tables has been compiled to aid the designer in choosing the correct hardware to match a particular application. These tables include seven segment decoder/drivers, digit drivers, LSI chips designed for use with LEDs, printed circuit board edge connectors, and filtering materials.

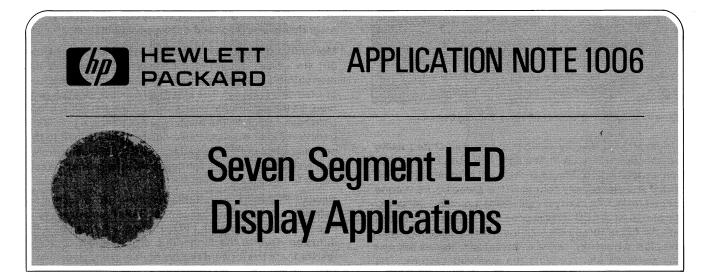

Figure 1. Large Seven Segment Display

#### LARGE SEVEN SEGMENT DISPLAYS

The large seven segment displays are designed to be easy to read single digit LED devices (Figure 1). They are typically used in electronic instruments, point-of-sale terminals, weighing scales, digital clocks, televisions, and appliances. The colors available are standard red, high efficiency red, yellow, and green. The standard red product is made from Gallium Arsenide Phosphide (GaAsP) on a GaAsP substrate. Both the high efficiency red and yellow seven segment displays are made from GaAsP on a Gallium Phosphide (GaP) substrate. The green seven segment displays are made from GaP on a GaP substrate. The increased efficiency of the GaP material results in the high efficiency red, yellow, and green displays having 3 to 5 times the minimum luminous intensity of the standard red displays.

A wide range of character heights varying from 7.6 mm (0.3 inch) to 20.3 mm (0.8 inch) allow the designer to choose the correct size display for the desired viewing range. The information in Figure 2 can be used to determine which character size display should be used for easy readibility. The information has been compiled for a standard viewer (20/20 eyesight) in typical office ambient condition (100-1000 lux) with the displays driven at recommended data sheet values.

| Character Size      | Maximum Viewing Distance |

|---------------------|--------------------------|

| 7.6 mm (0.3 inch)   | 5 metres                 |

| 10.9 mm (0.43 inch) | 6 metres                 |

| 14.1 mm (0.56 inch) | 7.5 metres               |

| 20.3 mm (0.8 inch)  | 9 metres                 |

Figure 2. Large Seven Segment Display Viewing Distances

The large LED display devices are manufactured using the concept of stretching the light from an LED by diffusion and reflection. The LED chips are mechanically supported and electrically connected by a lead frame. A cone shaped reflecting cavity is cast inside a rectangular package above each LED. This is done using glass filled epoxy with the top of this cavity forming the stretched segment. The plastic housing, called a "scrambler," forms the display package and contains the segment cavities. The stretched segment displays offer a variety of colors, sizes, and good on/off contrast.

These seven segment display products are available in either common anode or common cathode configuration with either right hand or left hand decimal point. The displays can be either dc driven or operated in the strobed mode. The low forward voltage of the LEDs makes the displays inherently IC compatible. The  $\pm 1$  overflow digit in the 14.1 mm (0.56 inch) package style is available in both common anode and common cathode configurations. For all other large seven segment displays, a universal overflow  $\pm 1$  digit with right hand decimal point is available. The  $\pm 1$  overflow digit has each LED anode and cathode present on external pins for ease of use.

#### MONOLITHIC SEVEN SEGMENT DISPLAYS

The monolithic seven segment displays are small, low cost, low power, multi-digit LED devices. They are typically used in desktop calculators, hand held instruments, metering devices, and various consumer products. With character heights ranging from 2.5 mm (0.1 inch) to 4.4 mm (0.175 inch), the monolithic products provide a flexible family of seven segment displays. The 2.5 mm (0.1 inch) character height displays are designed for hand held applications, whereas the 4.4 mm (0.175 inch) displays can be easily read at distances up to 2 metres.

Monolithic displays differ from other types of LED displays in that the individual light emitting segments are formed by diffusing separate LED junctions on a single chip of GaAsP. Because GaAsP is relatively expensive, most monolithic displays are magnified to keep chip sizes small. In most cases, the monolithic display is magnified by an external lens to attain a viewable character size.

Monolithic displays can be classified into two basic categories according to whether the lens is of the immersion or non-immersion type. Immersion lenses are formed by molding a lens directly over the LED chip. Non-immersion lenses have at least one layer of air between the LED chip and the lens assembly. Monolithic displays constructed with immersion lenses (Figure 3a) are manufactured by die attaching the monolithic GaAsP chips to the lead frame. The die attach pad also forms the common cathode electrical connection to the monolithic chip. The aluminum contact for each segment on the monolithic chip is then wire bonded to the appropriate anode contact. The

completed device is then fully encapsulated in epoxy. The magnifying lens is formed during encapsulation.

Monolithic displays with non-immersion lenses (Figure 3b) are usually constructed by epoxy die attaching the monolithic GaAsP chips to a special high temperature printed circuit board. The electrical contact for each segment on the monolithic chip is wire bonded to the appropriate anode trace on the printed circuit board. A precision injection molded lens is then aligned and attached to the printed circuit board. This attachment is done using holes that were drilled during fabrication of the printed circuit board to ensure alignment.

Hewlett-Packard's monolithic displays are of common cathode configuration since the GaAsP substrate is n doped material and each LED junction is formed by a P+diffusion. Due to the monolithic display's low dynamic resistance in the forward region, multiplexing at relatively high peak current is possible while keeping forward voltage typically less than 1.8 volts. For this reason, long strings can be easily strobed.

Figure 3a. Immersion Lens Monolithic Display

Figure 3b. Non-Immersion Lens Monolithic Display

# DC DRIVE TECHNIQUES (Large Seven Segment Displays Only)

When seven segment displays aré dc driven, each character is continuously illuminated. This is usually done with one decoder/driver per character and is commonly used for short display strings. If the display length is sufficiently short, the cost of dc decoding may be less than that of strobing circuitry. The fact that the drivers need not handle high current levels is a distinct advantage of dc operation.

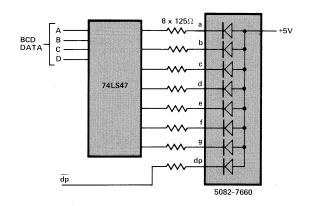

Figure 4a. DC Drive Circuit for the 5082-7660 Common Anode Display

Figure 4a shows the standard configuration for a common anode display. The current level, set here at 20 mA per segment, is determined by the relation

$$R = \frac{V_{CC} - V_F - V_{0(ON)}}{I_F} = \frac{5.0V - 2.2V - 0.35V}{20 \text{ mA}} = 125\Omega$$

where

V<sub>CC</sub> = voltage supply potential

$V_F$  = forward voltage of LED at desired IF  $V_{O(ON)}$  = ON state output voltage of display

driver (74LS47)

IF = desired forward current (20 mA)

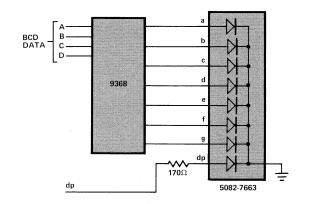

An analogous circuit is shown in Figure 4b for a common cathode display. The Fairchild 9368 is a seven segment decoder/driver incorporating input latches and constant 15 mA current outputs to directly drive common cathode LED displays.

Figure 4b. DC Drive Circuit for the 5082-7663 Common Cathode Display

# **MULTIPLEXED DRIVE TECHNIQUES**

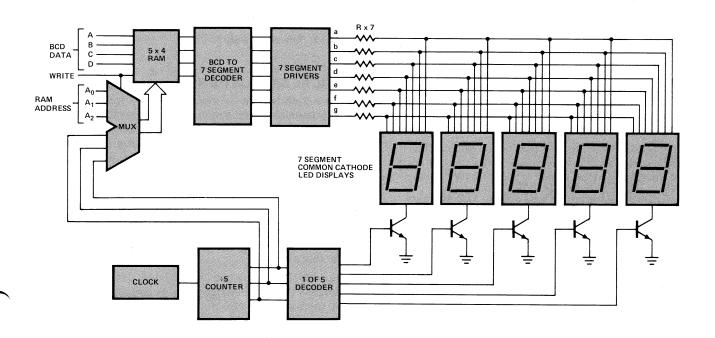

When multiplexing drive circuitry is used, the decoder is timeshared among digits in the display. The digits are electrically connected with like segments wired in parallel. This forms a seven (seven segments) by N (number of digits) array. In operation, the appropriate segment enable lines are activated for the particular character to be displayed. Simultaneously, a digit enable line is selected so that the character appears at the proper digit location. The strobe then progresses to the next digit position, activating the proper segments and digit enable line for that position. Figure 5 contains a block diagram of a typical five digit multiplexed LED display.

Since the eye is a relatively slow time average sensor, a viewer will perceive a repetitive visual phenomenon to be continuous if it occurs at a rate in excess of about 60 events per second. Therefore, if the refresh rate for each digit is maintained at 100 times or more per second, the perceived display will appear flicker-free and easy to read.

Figure 5. Block Diagram of a Multiplexed Five Digit LED Display

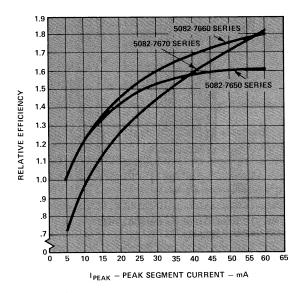

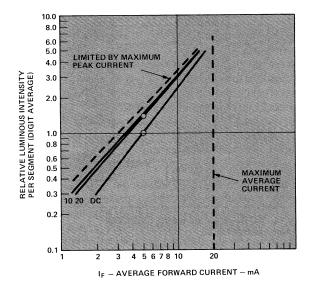

Figure 6a. Relative Luminous Efficiency (Luminous Intensity per Unit Current) vs. Peak Segment Current

In displays subject to vibration, a minimum strobe rate of five times the vibration frequency should be maintained.

In addition to reducing the number of decoders and drivers, strobing requires less power than dc drive to achieve the same display intensity. This is due to a basic property of GaAsP where luminous efficiency (light output/unit current) increases with the peak current level (see Figure 6a). Thus, for the same average current, the use of lower duty cycles and higher peak current levels results in increased light output. This phenomenon is illustrated in Figure 6b. Notice that the graph is normalized to one at a forward current of 5 mA dc. If this same device were operated at 25 mA peak, 20% duty factor (as if in a five digit strobed display) the time averaged luminous intensity would increase 40%.

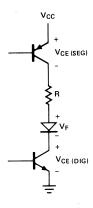

For common decoder/driver circuits, a series resistor is placed in each segment line to limit the LED current. This is done to prevent uneven current distribution among segments. Referring to Figure 7, the current limiting resistor values may be calculated using the following formula:

$$R = \frac{V_{CC} - V_{CE (SEG)} - V_{F} - V_{CE (DIG)}}{I_{PEAK}}$$

where

V<sub>CC</sub> = voltage supply potential

$V_{CE\ (SEG)} = saturation\ voltage\ drop\ across\ segment$

driver at IPEAK

V<sub>F</sub> = LED forward voltage at IPEAK

V<sub>CE</sub> (DIG) = saturation voltage drop across digit driver

at [IPEAK x 8 (worst case number of

segments ON)]

IPEAK = IAVERAGE x number of digits = peak LED

segment current

OR

$$I_{PEAK} = \frac{I_{AVG}}{D.F.}$$

Figure 6b. Relative Luminous Intensity per Segment vs. Average Current (5082-7650)

Figure 7. Typical Segment

# TYPICAL APPLICATIONS

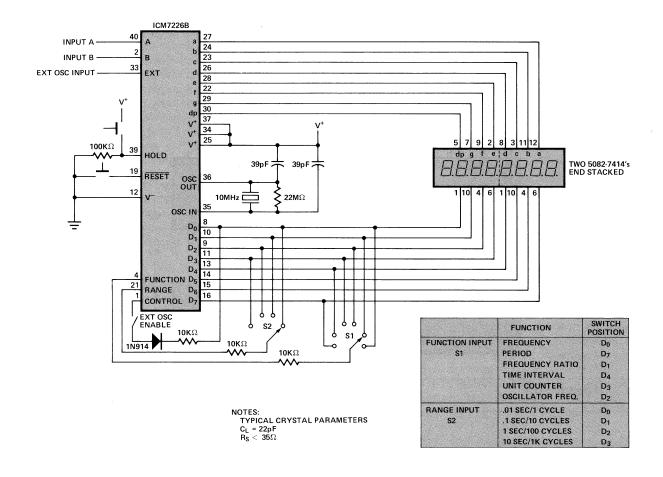

Figure 8 shows the complete circuitry for a minimum component universal counter. The Intersil ICM7226B is a fully integrated universal counter and LED display driver. It combines a high frequency oscillator, a decade time-base counter, an eight decade data counter with latches, a seven segment decoder, a digit multiplexer, and eight segment and eight digit drivers that drive monolithic LEDs directly. If the designer wishes to use the ICM7226A or B (common anode or cathode) to drive large seven segment products, he should consider his application carefully because higher drive currents are required to produce a readable display.

The ICM7226B updates the segment information and refreshes the common cathode displays at an IPEAK of 15 mA/segment on a 12% duty cycle. This drive current is ideal for the monolithic seven segment family. The circuit in Figure 8 employs two 5082-7414 monolithic devices as the display portion of the counter. Typical devices will exhibit a 30  $\mu$ cd time averaged luminous intensity, thus

Figure 8. 10 MHz Universal Counter

providing excellent readability. Combining the compactness of the monolithic displays and the complexity of the single chip universal counter system, an extremely powerful hand held instrument can be realized.

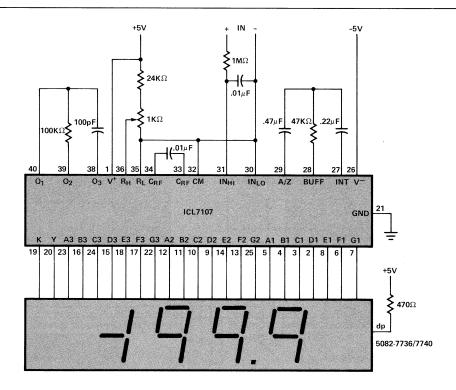

Figure 9 shows the circuitry necessary for a high performance, low power 3-1/2 digit panel meter. The circuit utilizes the Intersil ICL7107 (CMOS) A/D converter, seven passive components, and four large seven segment displays. All necessary active devices are contained on the chip. This includes seven segment decoders, display drivers, a reference voltage, and a clock.

The ICL7107 is designed to dc drive 3 seven segment displays and one overflow digit at a typical forward current of 8 mA per segment. The segment information is decoded and updated continuously by the control logic within the chip. The 7.6mm (0.3 inch) standard red displays (5082-7736/-7740) provide an attractive display for this low cost digital panel meter. For higher light output, the high efficiency red, yellow, or green displays can be used.

# MICROPROCESSOR DISPLAY INTERFACE TECHNIQUES

The four basic techniques for interfacing microprocessors to seven segment displays are listed below:

1. The DC Driven Controller statically drives an LED

- seven segment display from a microprocessor output port. In the standard configuration, each display is assigned a different address so that a Memory or I/O Write to that address changes the contents of the corresponding display digit.

- The Refresh Controller interfaces the microprocessor to a multiplexed LED display. The controller periodically interrupts the microprocessor and after each interrupt, the microprocessor supplies new display data for the next refresh cycle of the display.

- 3. The Decoded Data Controller refreshes a multiplexed LED display independently from the microprocessor system. The local RAM stores decoded display data. This data is continuously read from the RAM and then used to refresh the display. Whenever the display message is changed, the microprocessor decodes each character in software and writes the decoded data into the local RAM.

- 4. The Coded Data Controller also refreshes a multiplexed LED display independently from the microprocessor system. The local RAM stores BCD data which is continuously read, decoded, and used to refresh the display. The display message is changed by writing new BCD characters into the local RAM.

Figure 9. 3-1/2 Digit Voltmeter

Figure 10. DC Driven Controller

#### DC DRIVEN CONTROLLERS

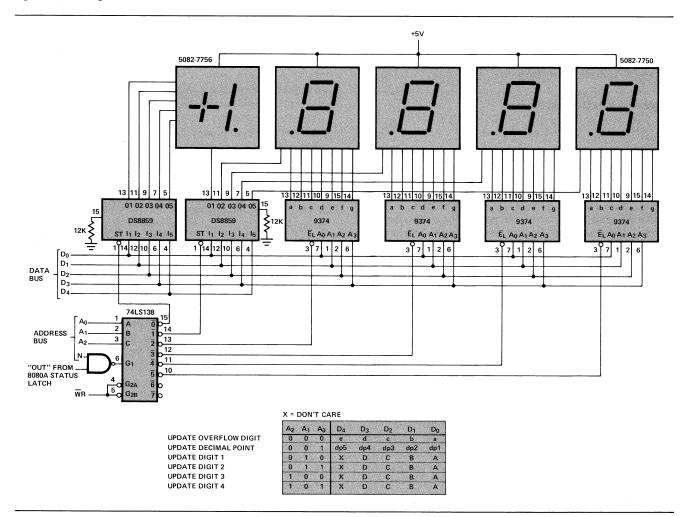

When the seven segment display is driven on a dc basis, a seven segment decoder/driver or latch is required for each display. Figure 10 shows an example of a seven segment display to microprocessor interface. Each display is driven by its own seven segment driver. The Fairchild 9374 has current sink outputs that drive each LED segment at 15 mA dc. The decimal points and overflow digit are driven by two National DS 8859's. These hex latches have programmable current sink outputs. The Intel 8080A microprocessor updates each display with an OUTput instruction which accesses up to 256 output devices and ports.

Upon execution of the OUTput instruction, the lower five bits of the accumulator are loaded into the DS8859 associated with the overflow digit. Next, the decimal point is updated in a similar fashion. Finally, the four decoder/drivers are successively loaded with the correct BCD information.

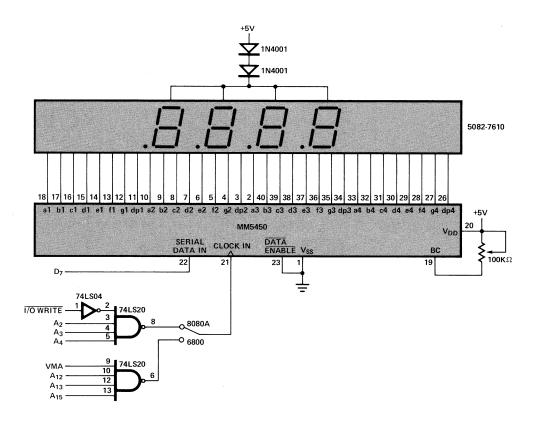

Figure 11 shows a DC Driven Controller utilizing the National MM5450 LED Display Driver. The MM5450 is a serial in-parallel out shift register with 34 output pins that can sink up to 15 mA each. It is specifically designed to operate with common anode displays and minimal interface with the source of data. Serial data transfer from the data source, in this case the microprocessor, to the display driver is accomplished with two signals. These signals are SERIAL DATA and CLOCK. By using a format of a leading "1" bit followed by the 35 data bits, data transfer

is allowed without any additional handshaking signals. The 35 data bits are latched after the 36th bit is complete. This provides non-multiplexed, direct drive to the seven segment displays.

Figures 12a and 12b contain the software necessary to interface the MM5450 to the 6800 and 8080A microprocessors respectively. The serial display data is transferred to the microprocessor via bit 7 of the Data Bus. The data is clocked in each time the microprocessor writes to the MM5450. In the case of the 8080A, this is done with the I/O WRITE signal and a combination of lower ordered addresses. The 6800 accomplishes this task with the VMA signal and a combination of higher address bits. The decoded segment data is assumed to be in four successive memory bytes starting at location \$0006. The format of the decoded segment data for all microprocessor interfaces in this note is shown in Figure 13.

The software first outputs a start bit to the MM5450. Next, the first digit's segment information is clocked into MM5450. The segment information is then rotated left eight times with this data being clocked into the display after each shift. This procedure is repeated for each digit, thus providing 33 clock pulses (the start bit plus (4x8) segment bits). In order for the segment data to be latched to the display, a complete set of 36 clocks must occur. For this reason, there are three dummy clocks at the end of the program. The term "dummy" is used because the data that is being clocked into MM5450 never appears on the seven segment display.

Figure 11. DC Driven Controller with Serial Data Interface to 6800 and 8080A

|       |            | <b>B</b> 0 | 00   | DSPLY | EQU   | \$B000     |                                        |

|-------|------------|------------|------|-------|-------|------------|----------------------------------------|

| 0006  |            |            |      |       | ORG   | \$0006     |                                        |

| 0006  |            |            |      | DATA  | RMB   | \$4        |                                        |

| 0000  |            |            |      | DAIA  | KNID  | J+         |                                        |

| 0400  |            |            |      |       | ORG   | \$0400     |                                        |

| 0400  | CE         | 00         | 06   | LOAD  | LDX   | I.DATA     |                                        |

| 0403  |            | 80         | 00   | LOND  | LDA A | - 1 T - 12 | LOAD START BIT                         |

| 0405  | B7         | B0         | 00   |       |       | E,DSPLY    | OUTPUT START BIT                       |

|       |            |            | . 00 | CTART |       |            | INITIALIZE COUNTER                     |

| 0408  | C6         |            |      | START | LDA B |            |                                        |

| 040A  | <b>A</b> 6 |            |      |       | LDA A |            | LOAD DATA                              |

| 040C  | <b>B</b> 7 | <b>B</b> 0 | 00   | LOOP  | STA A | E,DSPLY    | OUTPUT DATA TO DISPLAY                 |

| 040F  | 49         |            |      |       | ROL A |            | ROTATE TO NEXT BIT                     |

| 0410  | 5A         |            |      |       | DEC B |            | DECREMENT COUNTER                      |

| 0411  | 26         | F9         |      |       | BNE   | LOOP       | BRANCH IF NOT DONE, ELSE CONTINUE      |

| 0413  | 08         |            |      |       | INX   |            |                                        |

| 0414  | 8C         | 00         | 04   |       | CPX   | 1,\$04     | LAST WORD?                             |

| 0417  | 26         | EF         |      |       | BNE   | START      | BRANCH IF NOT LAST WORD, ELSE CONTINUE |

| 0419  | <b>B</b> 7 | <b>B</b> 0 | 00   |       | STA A | E,DSPLY    | DUMMY CLOCK 1                          |

| 041C  | <b>B</b> 7 | BO         | 00   |       | STA A | E,DSPLY    | DUMMY CLOCK 2                          |

| 041F  | <b>B</b> 7 | B0         | 00   |       |       | E.DSPLY    | DUMMY CLOCK 3, SEG DATA LATCHED        |

| 0422  | 39         |            |      |       | RTS   |            |                                        |

| 0 122 | ,          |            |      |       |       |            |                                        |

Figure 12a. 6800 Interface to DC Drive Controller Shown in Figure 11

| E000 |          | DSPLY | EQU   | 001CH  |                                      |

|------|----------|-------|-------|--------|--------------------------------------|

| E000 |          |       | ORG   | 0E006H |                                      |

| E006 |          | DATA  | DS    | 4      |                                      |

| E00A |          |       | ORG   | 0E400H |                                      |

| E400 | 3E 80    | LOAD  | MVI   | A,80H  | LOAD START BIT                       |

| E402 | D3 1C    |       | OUT   | DSPLY  | OUTPUT START BIT                     |

| E404 | 21 06 E0 |       | LXI   | H,DATA | GET ADDRESS OF SEG DATA              |

| E407 | 06 08    | START | MVI   | B,08H  | INITIALIZE COUNTER                   |

| E409 | 7E       |       | MOV   | A,M    | LOAD SEG DATA                        |

| E40A | D3 1C    | LOOP  | OUT   | DSPLY  | OUTPUT SEG DATA TO DISPLAY           |

| E400 | 07       |       | RLC   |        | ROTATE TO NEXT BIT                   |

| E40D | 05       |       | DCR   | В      | DECREMENT COUNTER                    |

| E40E | 02 0A E4 |       | JNZ   | LOOP   | JUMP IF NOT DONE, ELSE CONTINUE      |

| E411 | 2C       |       | INR L |        |                                      |

| E412 | 7D       |       | MOV   | A,L    |                                      |

| E413 | FE 0A    |       | CPI   | 0AH    | LAST WORD?                           |

| E415 | C2 07 E4 |       | JNZ   | START  | JUMP IF NOT LAST WORD, ELSE CONTINUE |

| E418 | D3 1C    |       | OUT   | DSPLY  | DUMMY CLOCK I                        |

| E419 | D3 1C    |       | OUT   | DSPLY  | DUMMY CLOCK 2                        |

| E41C | D3 1C    |       | OUT   | DSPLY  | DUMMYCLOCK 3, SEG DATA LATCHED       |

| E41E | C9       |       | RET   |        |                                      |

|      |          |       |       |        |                                      |

Figure 12b. 8080A Interface to DC Driven Controller Shown in Figure 11

|   |   |   |   |   |   | D <sub>1</sub> |    |

|---|---|---|---|---|---|----------------|----|

| а | b | С | d | е | f | g              | dp |

Figure 13. Format for Decoded Segment Data

The 5082-7610 7.6mm (0.3 inch) high efficiency red displays driven at 15 mA/segment dc provide a large, easy to read, four digit display. The 100 K $\Omega$  potentiometer sets a reference current for the LEDs and provides brightness control for applications in varying ambients.

#### REFRESH CONTROLLER

The Refresh Controller uses the microprocessor to actively strobe the display. This strobing is accomplished via an interrupt that causes the microprocessor to service the refresh subroutine. The refresh program provides new segment and digit information for the display. This application note shows two types of Refresh Controllers. The basic difference between the controllers is the nature of data that is transferred from the microprocessor to the controller. The first type (Figure 14) requires eight data lines to transfer the decoded segment and decimal point information. The second type of Refresh Controller (Figure 15) requires only five data lines to interface to the microprocessor. The data is transferred using BCD data and a decimal point bit. The technique for digit strobing also is slightly different due to the difference in display length.

Figure 14. Sunlight Viewable Refresh Controller

Figure 15. Refresh Controller

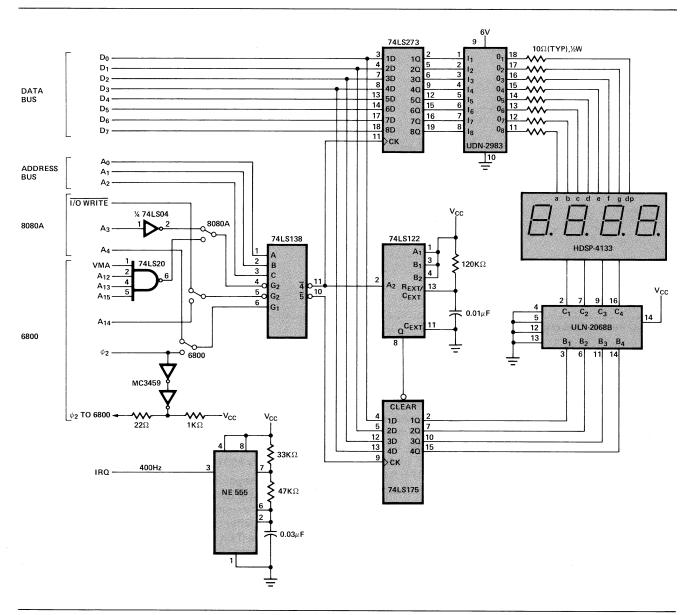

The circuit in Figure 14 utilizes the 10.9mm (0.43 inch) yellow HDSP-4133 seven segment displays. These displays are readable in direct sunlight when driven near the data sheet maximums as they are in Figure 14. The Sprague segment drivers are sourcing 120 mA peak on a 1/4 duty factor. The ULN-2068B can sink a maximum of 1.75A and therefore is an excellent digit driver as the maximum digit current is (120 mA) (8 segments)  $\cong$  1 Amp. The retriggerable monostable multivibrator (74LS122) senses strobing activity on the segment lines. If the strobing stops for any reason (microprocessor crash, etc.), the digit drivers are turned off immediately. This protects the displays from the 120 mA dc they would pass if the strobing ceased.

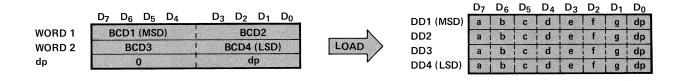

Figure 16a and 16b contain the software necessary to interface the Refresh Controller in Figure 14 to the 6800 and the 8080A microprocessors respectively. The programs consist of two subroutines. The first subroutine LOAD is called by the user's main program. LOAD should

be called the first time data is to be displayed and any time when new display data is desired. This subroutine assumes the user has stored three consecutive bytes of BCD data and decimal point information in locations WORD1, WORD2, and DP. The subroutine unpacks the coded data stored in these locations, decodes it into segment data, and stores it in locations DD1, DD2, DD3, and DD4. Figure 16c graphically shows the effect of the subroutine LOAD.

LOAD uses a segment data lookup table located in ROM. The lookup table consists of sixteen successive locations that contain the segment information for displaying numbers 0-9 and letters A-F. A 1 bit corresponds to an ON segment and a 0 bit to an OFF segment. All dp bits have been programmed to a logical 0 in the lookup table. Subroutine LOAD assumes that only one decimal point will be ON in the four digit string. The code beginning with label DCPT determines which digit should display a decimal point and changes the dp bit to a logical 1. The subroutine is now complete and control returns to the main program.

```

EQU

EQU

RMB

BF 04

SEG

$BF04

DIG

POINT

DIGIT

RMB

0003

0004

WORDI

WORD2

RMB

RMB

RMB

0005

DP

0005

0006

0007

DDI

DD2

RMB

0008

0009

DD3

DD4

RMB

0400

0400

CE 06

00

LOAD

LDX

1.$0600

STX

LDA

STA

LDA

TAB

D,POINT

A I,$01

A D,DIGIT

A D,WORDI

0403

DF 00

86 01

97 02

96 03

16

54

54

54

D7 01

DE 00

INITIALIZE POINTER

INITIALIZE DIGIT

LOAD 2 BCD WORDS

MAKE A COPY

0409

LSR

RIGHT JUSTIFY BCD1

040D

LSR

LSR

B D,POINT+1

D,POINT

040F

LSR

0410

0412

STA

LDX

POINT TO DIGIT I SEG. DATA

B X,0

B D,DDI

0414

E6 00

D7 06

84 0F

97 01

DE 00

A6 00

97 07

96 04

16

LDA

STA

LOAD DIGIT I SEG. DATA

STORE DIGIT I SEG. DATA

AND

STA

LDX

A I,$0F

A D,POINT+1

D,POINT

0418

MASK LEAVING BCD2

041A

041C

041E

POINT TO DIGIT 2 SEG. DATA

A X,0

LOAD DIGIT 2 SEG. DATA

STORE DIGIT 2 SEG. DATA

LOAD NEXT 2 BCD WORDS

LDA

STA

LDA

A D,DD2

A D,WORD2

0420

0422

0424

MAKE A COPY

RIGHT JUSTIFY BCD3

TAB

LSR

LSR

0425

54

54

D7 01

0427

LSR

LSR

LSR

STA

LDX

LDA

STA

0428

0429

B D,POINT+1

DE 00

E6 00

D7 08

D,POINT

B X,0

042B

POINT TO DIGIT 3 SEG. DATA

LOAD DIGIT 3 SEG. DATA

STORE DIGIT 3 SEG. DATA

MASK LEAVING BCD4

B D.DD3

042F

0431

0433

0435

84 0F

97 01

DE 00

AND

STA

A 1,$0F

A D,POINT+1

POINT TO DIGIT 4 SEG. DATA

LDX

D,POINT

A6 00

97 09

96 05

CE 00

A X,0

A D,DD4

A D,DP

0437

LDA

STA

LOAD DIGIT 4 SEG. DATA

STORE DIGIT 4 SEG. DATA

043B

DCPT

LDA

LOAD DIGIT THAT NEEDS DP (1, 2, 3, 4)

043D

0440

LDX

INX

CLEAR INDEX REG

INCR

08

4A

0441

DEC

BNE

26 FC

A6 05

8B 01

A7 05

39

0442

0444

INCR

LOOP TRANSFERS DP DATA TO INDEX REG

A X,DP

LDA

LOAD THE SEG. DATA NEEDING DP

ADD

STA

RTS

0446

0448

A I,$01

A X,DP

GIVE IT A DP

STORE IT BACK

044A

044B

0F

RFRSH

SEI

DISABLE INTERRUPTS DURING REFRESH

D6 02

C1 01

26 05

CE 00 06

B D,DIGIT

044C

LDA

FIND OUT WHICH DIGIT

044E

0450

CMP

BNE

B I,$01

NFST

IS IT DIGIT 1?

BRANCH IF NOT FIRST, ELSE CONTINUE

0452

LDX

L$0006

DF 00

86 00

B7 BF 05

DE 00

0455

0457

D,POINT

INITIALIZE POINTER TO DDI

CLEAR A

BLANK DISPLAY

POINT TO SEG. DATA

LOAD SEG. DATA

OUTPUT SEG. DATA TO DISPLAY

OUTPUT DIGIT DATA TO DISPLAY

OUTPUT ACT DIGITS

NFST

LDA

A 1,$00

0459

045C

045E

STA

LDX

A E,DIG

D,POINT

A6 00

B7 BF 04

F7 BF 05

C1 08

27 08

78 00 02

7C 00 01

A X,0

A E,SEG.

B E,DIG

LDA

0460

0463

0466

0468

046A

046D

STA

STA

CMP

BEQ

IS IT THE LAST DIGIT?

BRANCH IF LAST, ELSE CONTINUE

SHIFT TO NEXT DIGIT

B 1,$08

LOOPI

E,DIGIT

ASL

INC

E.POINT+I

POINT TO NEXT SEG. DATA

0470

0471

RE-ENABLE INTERRUPTS

3B

RETURN

0472

86 01

97 02

LOOPI

LDA

A 1,$01

A D,DIGIT

RE-INITIALIZE TO DIGIT I

STA

CLI

0474

0476

RE-ENABLE INTERRUPTS

0E

0477

RTI

ORG

0600

$0600

0600

0601

FCB

FCB

$60

0602

0603

0604

FCB

FCB

FCB

DA

F2

66

B6

3E

$DA

$F2

$66

FCB

FCB

FCB

$B6

$3E

0605

0606

0607

E0

FE

$E0

0608

$FE

E6

EE

060A

FCB

SEE

060B

060C

FCB

FCB

$90

9C

7A

060D

FCB

FCB

$7A

$9E

D

E

F

060F

```

Figure 16a. 6800 Interface to Refresh Controller in Figure 14

| E000<br>E000                 |                      | SEG<br>DIG              | EQU<br>EQU            | 001CH<br>001DH    |                                                               |

|------------------------------|----------------------|-------------------------|-----------------------|-------------------|---------------------------------------------------------------|

| E000<br>E000<br>E002<br>E003 |                      | POINT<br>DIGIT<br>WORDI | ORG<br>DS<br>DS<br>DS | 0E000H<br>2<br>1  |                                                               |

| E004<br>E005                 |                      | WORD2<br>DP             | DS<br>DS              | 1                 |                                                               |

| E006                         |                      | DDI                     | DS                    | 1                 |                                                               |

| E007<br>E008                 |                      | DD2<br>DD3              | DS<br>DS              | 1                 |                                                               |

| E009                         |                      | DD3<br>DD4              | DS                    | 1                 |                                                               |

| E00A                         |                      |                         | ORG                   | 0E400H            |                                                               |

| E400                         | 21 00 E6             | LOAD                    | LXI                   | H, 0E600H         |                                                               |

| E403<br>E406                 | 22 00 E0<br>3E 01    |                         | SHLD                  | POINT             | INITIALIZE POINTER                                            |

| E408                         | 3E 01<br>32 02 E0    |                         | MVI<br>STA            | A, 01H<br>DIGIT   | INITIALIZE DIGIT                                              |

| E40B                         | 3A 03 E0             |                         | LDA                   | WORDI             | LOAD 2 BCD WORDS (BCD1, BCD2)                                 |

| E40E<br>E410                 | E6 F0<br>0F          |                         | ANI<br>RRC            | 0F0H              | MASK OUT LOWER NIBBLE<br>RIGHT JUSTIFY BCDI                   |

| E411                         | 0F                   |                         | RRC                   |                   |                                                               |

| E412<br>E413                 | 0F<br>0F             |                         | RRC<br>RRC            |                   |                                                               |

| E414                         | 6F                   |                         | MOV                   | L, A              | POINT TO DIGIT 1 SEG. DATA                                    |

| E415<br>E416                 | 7E<br>32 06 E0       |                         | MOV<br>STA            | A,M<br>DDI        | LOAD DIGIT I SEG. DATA<br>STORE DIGIT I SEG. DATA             |

| E419                         | 3A 03 E0             |                         | LDA                   | WORDI             | LOAD SAME 2 BCD WORDS (BCD1, BCD2)                            |

| E41C<br>E41E                 | E6 OF<br>6F          |                         | ANI<br>MOV            | 0FH<br>L, A       | MASK OUT UPPER NIBBLE POINT TO DIGIT 2 SEG. DATA              |

| E41F                         | 7E                   |                         | MOV                   | A, M              | LOAD DIGIT 2 SEG. DATA                                        |

| E420<br>E423                 | 32 07 E0<br>3A 04 E0 |                         | STA<br>LDA            | DD2<br>WORD2      | STORE DIGIT 2 SEG. DATA<br>LOAD NEXT 2 BCD WORDS (BCD3, BCD4) |

| E426                         | E6 F0                |                         | ANI                   | 0F0H              | MASK OUT LOWER NIBBLE                                         |

| E428<br>E429                 | 0F<br>0F             |                         | RRC<br>RRC            |                   | RIGHT JUSTIFY BCD3                                            |

| E42A                         | 0F                   |                         | RRC                   |                   |                                                               |

| E42B<br>E42C                 | 0F<br>6F             |                         | RRC<br>MOV            | L,A               | POINT TO DIGIT 3 SEG. DATA                                    |

| E42D                         | 7E                   |                         | MOV                   | A, M              | LOAD DIGIT 3 SEG. DATA                                        |

| E42E<br>E431                 | 32 08 E0<br>3A 04 E0 |                         | STA<br>LDA            | DD3<br>WORD2      | STORE DIGIT 3 SEG. DATA<br>LOAD SAME 2 BCD WORDS (BCD3, BCD4) |

| E434                         | E6 0F                |                         | ANI                   | 0FH               | MASK OUT UPPER NIBBLE                                         |

| E436<br>E437                 | 6F<br>7E             |                         | MOV<br>MOV            | L, A<br>A, M      | POINT TO DIGIT 4 SEG. DATA LOAD DIGIT 4 SEG. DATA             |

| E438                         | 32 09 E0             |                         | STA                   | DD4               | STORE DIGIT 4 SEG. DATA                                       |

| E43B<br>E43E                 | 3A 05 E0<br>01 05 E0 | DCPT                    | LDA<br>LXI            | DP<br>B,0E005H    | LOAD DIGIT NEEDING DP<br>SET BC REG PAIR AS A POINTER         |

| E441                         | 03                   | INCR                    | INX                   | В                 | LOOP TRANSFERS DP DATA TO BC                                  |

| E442<br>E443                 | 3D<br>C2 41 E4       |                         | DCR<br>JNZ            | A<br>INCR         |                                                               |

| E446                         | 0A                   |                         | LDAX                  | В                 | LOAD SEG. DATA NEEDING DP                                     |

| E447<br>E449                 | C6 01<br>02          |                         | ADI<br>STA X          | OIH<br>B          | GIVE IT A DP<br>STORE IT BACK                                 |

| E44A                         | C9                   |                         | RET                   |                   |                                                               |

| E44B                         | F3                   | RFRSH                   | DI                    |                   | DISABLE INTERRUPTS                                            |

| E44C<br>E44D                 | F5<br>E5             |                         | PUSH<br>PUSH          | PSW<br>H          | SAVE ON STACK                                                 |

| E44E                         | D5                   |                         | PUSH                  | n<br>D            |                                                               |

| E44F<br>E452                 | 3A 02 E0<br>FE 01    |                         | LDA                   | DIGIT             | FIND OUT WHICH DIGIT<br>LAST DIGIT?                           |

| E454                         | C2 5D E4             |                         | CPI<br>JNZ            | 01H<br>NFST       | JUMP IF NOT FIRST, ELSE CONTINUE                              |

| E457<br>E45A                 | 21 06 E0<br>22 00 E0 |                         | LXI<br>SHLD           | H,0E006H<br>POINT | HL REG RE-INITIALIZED POINT POINTS TO DDI                     |

| E45D                         | 3E 00                | NFST                    | MVI                   | A, 00H            |                                                               |

| E45F<br>E461                 | D3 1D<br>2A 00 E0    |                         | OUT<br>LHLD           | DIG<br>POINT      | BLANK DISPLAY POINT POINTS TO SEG. DATA                       |

| E464                         | EB                   |                         | XCHG                  |                   | SWAP                                                          |

| E465<br>E466                 | IA<br>EB             |                         | LDAX<br>XCHG          | D                 | LOAD SEG. DATA VIA DE PAIR<br>SWAP BACK                       |

| E467                         | D3 IC                |                         | OUT                   | SEG               | OUTPUT SEG. DATA TO DISPLAY                                   |

| E469<br>E46C                 | 3A 02 E0<br>D3 1D    |                         | LDA<br>OUT            | DIGIT<br>DIG      | LOAD DIGIT DATA OUTPUT DIGIT DATA TO DISPLAY                  |

| E46E                         | FE 08                |                         | CPI                   | 08H               | LAST DIGIT?                                                   |

| E470<br>E473                 | CA E4 80<br>07       |                         | JZ<br>RLC             | LOOPI             | JUMP IF LAST, ELSE CONTINUE<br>ROTATE TO NEXT DIGIT           |

| E474<br>E477                 | 32 02 E0<br>23       |                         | STA                   | DIGIT<br>H        | STORE FOR NEXT DIGIT INCREMENT                                |

| E478                         | 22 00 E0             | LOOP2                   | SHLD                  | POINT             | POINT POINTS TO NEXT SEG. DATA                                |

| E47B                         | DI                   |                         | POP                   | D                 | SAVE IT                                                       |

| E47C<br>E47D                 | EI<br>FI             |                         | POP<br>POP            | H<br>PSW          |                                                               |

| E47E<br>E47F                 | FB<br>C9             |                         | EI<br>RET             |                   | ENABLE INTERRUPTS                                             |

| E480                         | 3F 01                | LOOP1                   | MVI                   | A, 01H            | RETURN                                                        |

| E482<br>E485                 | 32 02 E0<br>C3 78 E4 |                         | STA                   | DIGIT             | DIGIT POINTS TO DIGIT I                                       |

| 1.403                        | C3 /0 E4             |                         | JMP                   | LOOP2             |                                                               |

| E600                         | FC                   |                         | ORG<br>DB             | 0E600<br>0FCH     | 0                                                             |

| E601                         | 60                   |                         | DB                    | 060H              | 1                                                             |

| E602<br>E603                 | DA<br>F2             |                         | DB<br>DB              | 0DAH<br>0F2H      | 2 3                                                           |

| E604                         | ,66                  |                         | DB .                  | 066H              | 4                                                             |

| E605<br>E606                 | B6<br>3E             |                         | DB<br>DB              | 0B6H<br>03EH      | 5                                                             |

| E607                         | E0                   |                         | DB                    | 0E0H              | 7                                                             |

| E608                         | FE<br>E6             |                         | DB                    | 0FEH              | 8                                                             |

| E609<br>E60A                 | E6<br>EE             |                         | DB<br>DB              | 0E6H<br>0EEH      | 9<br>A                                                        |

| E60B<br>E60C                 | 3E<br>9C             |                         | DB<br>DB              | 03EH<br>09CH      | B<br>C                                                        |

| E60D                         | 7 <b>A</b>           |                         | DB                    | 07AH              | D                                                             |

| E60E<br>E60F                 | 9E<br>8E             |                         | DB<br>DB              | 09EH<br>08EH      | Б                                                             |

| 2.001                        | '                    |                         | 20                    |                   | •                                                             |

Figure 16b. 8080A Interface to Refresh Controller in Figure 14

Upon interruption by the 555 timer, the microprocessor is vectored to service the routine RFRSH. This routine uses the register POINT to locate segment information (DD1, DD2, DD3 and DD4) to be output to the display. Label SEG is the address to which segment data is to be written. The label DIG is used in a similar manner to identify the address where digit data is to be written. RFRSH updates the display by first blanking all segments. This interdigit blanking eliminates the phenomenon of partially illuminated segments known as ghosting. Next, segment information is written to the octal latch (74LS273). Finally, the digit information is written to the quad latch (74LS175). Control is then returned to the main program. This process is repeated with the correct segment information for each of the four digits.

With proper display filtering, the circuit in Figure 12 controlled by either the 6800 or 8080A programs provides an excellent four digit, sunlight viewable display.

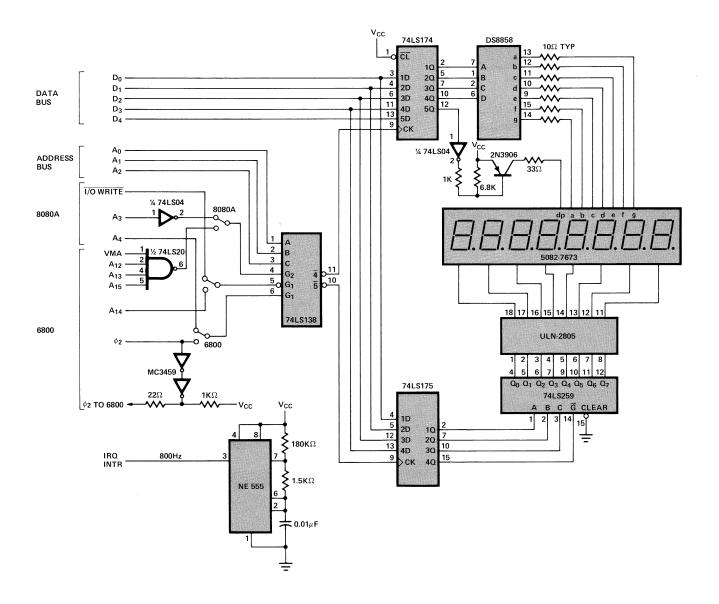

The Refresh Controller shown in Figure 15 is quite similar to the circuit in Figure 14. However, there are a few minor differences that should be pointed out. The Refresh Controller in Figure 15 utilizes the National DS8858 BCD-toseven segment decoder driver. This enables the user to write BCD data to the Refresh Controller without utilizing the LOAD subroutine. This saves both RAM space and microprocessor time. The software to interface this Refresh Controller to the 6800 and the 8080A microprocessors is shown in Figures 17a and 17b respectively. The circuit uses the green 5082-7673 large seven segment common cathode displays.

(WORD 1, WORD, AND dp ARE CONSECUTIVE RAM LOCATIONS)

(DD1, DD2, DD3, AND DD4 ARE CONSECUTIVE RAM LOCATIONS)

Figure 16c. Subroutine LOAD

|      | BF         | 04 |    | SEG   | EQU  |   | \$BF04    |                                     |

|------|------------|----|----|-------|------|---|-----------|-------------------------------------|

|      | BF         | 05 |    | DIG   | EQU  |   | \$BF04    |                                     |

| 0000 |            |    |    | POINT | RMB  |   | 2         |                                     |

| 0002 |            |    |    | DIGIT | RMB  |   | 1         |                                     |

| 0003 |            |    |    | DATA  | RMB  |   | 8         |                                     |

|      |            |    |    |       |      |   |           |                                     |

| 0400 |            |    |    |       | ORG  |   | \$0400    |                                     |

| 0400 | CE         | 00 | 03 | INIT  | LDX  |   | I,\$0003  |                                     |

| 0403 | DF         | 00 |    |       | STX  |   | D,POINT   | INITIALIZE POINT                    |

| 0405 | 7F         | 00 | 02 |       | CLR  |   | E.DIGIT   | INITIALIZE DIGIT                    |

| 0408 | 0F         |    |    | RFRSH | SEI  |   |           | DISABLE INTERRUPTS                  |

| 0409 | DE         | 00 |    |       | LDX  |   | D,POINT   | GET POINT                           |

| 040B | E6         | 00 |    |       | LDA  | В | X,0       |                                     |

| 040D | 86         | 08 |    |       | LDA  |   | 1,\$08    |                                     |

| 040F | B7         | BF | 05 |       | STA  |   | E,DIG     | BLANK DISPLAY                       |

| 0412 | F7         | BF | 04 |       | STA  |   | E,SEG     | OUTPUT SEG. DATA TO DISPLAY         |

| 0415 | 96         | 02 |    |       | LDA  | Α | D.DIGIT   | GET DIGIT                           |

| 0417 | 81         | 07 |    |       | CMP  | Α | I.\$07    |                                     |

| 0419 | 27         | 0B |    |       | BEQ  |   | LOOP1     | BRANCH IF LAST DIGIT, ELSE CONTINUE |

| 041B | 7C         | 00 | 02 |       | INC  |   | E,DIGIT   | INCREMENT TO NEXT DIGIT             |

| 041E | <b>B</b> 7 | BF | 05 |       | STA  | Α | E,DIG     | OUTPUT DIGIT DATA TO DISPLAY        |

| 0421 | 7C         | 00 | 01 |       | INC  |   | E,POINT+1 | POINT POINTS TO NEXT BCD WORD       |

| 0424 | 0E         |    |    |       | CLI  |   |           |                                     |

| 0425 | 3B         |    |    |       | RTI  |   |           |                                     |

| 0426 | B7         | BF | 05 | LOOPI | STA  | Α | E,DIG     | OUTPUT DIGIT DATA TO DISPLAY        |

| 0429 | CE         | 00 | 03 |       | LDX  |   | I,\$0003  |                                     |

| 042C | DF         | 00 |    |       | STX  |   | D.POINT   | RE-INITIALIZE POINT                 |

| 042E | 7F         |    | 02 |       | CLR  |   | E,DIGIT   | RE-INITIALIZE DIGIT                 |

| 0431 | 0E         |    |    |       | CLI  |   |           |                                     |

| 0432 | 3B         |    |    |       | RTI  |   |           |                                     |

|      |            |    |    |       | 2777 |   |           |                                     |

Figure 17a. 6800 Interface to Refresh Controller Shown in Figure 15

| E000 |    |    |    | SEG   | EQU  | 001CH        |                               |

|------|----|----|----|-------|------|--------------|-------------------------------|

| E000 |    |    |    | DIG   | EQU  | 001DH        |                               |

|      |    |    |    |       |      |              |                               |

| E000 |    |    |    |       | ORG  | 0E000H       |                               |

| E000 | 03 | E0 |    | POINT | DW   | DATA         |                               |

| E002 |    |    |    | DIGIT | DS   | 01H          |                               |

| E003 |    |    |    | DATA  | DS   | 08H          |                               |

|      |    |    |    |       |      |              |                               |

| E00B |    |    |    |       | ORG  | 0E400H       |                               |

| E400 | 21 | 03 | E0 | INIT  | LXI  | H,0E003H     |                               |

| E403 | 22 | 00 | E0 |       | SHLD | POINT        | INITIALIZE POINT              |

| E406 | 3E | 00 |    |       | MVI  | A,0          |                               |

| E408 | 32 | 02 | E0 |       | STA  | DIGIT        | INITIALIZE DIGIT              |

| E40B | F3 |    |    | RFRSH | DI   |              | DISABLE INTERRUPTS            |

| E40C | F5 |    |    |       | PUSH | PSW          | SAVE                          |

| E40D | E5 |    |    |       | PUSH | Н            | SAVE                          |

| E40E | 2A | 00 | E0 |       | LHLD | POINT        | GET POINT                     |

| E411 | 3E | 08 |    |       | MVI  | A,08H        |                               |

| E413 | D3 | 1D |    |       | OUT  | DIG          | BLANK DISPLAY                 |

| E415 | 7E |    |    |       | MOV  | A,M          |                               |

| E416 | D3 | 1C |    |       | OUT  | SEG          | OUTPUT SEG. DATA TO DISPLAY   |

| E418 | 3A | 02 | E0 |       | LDA  | DIGIT        | GET DIGIT                     |

| E41B | D3 | 1D |    |       | OUT  | DIG          | OUTPUT DIGIT DATA TO DISPLAY  |

| E41D | FE | 07 |    |       | CPI  | 07H          |                               |

| E41F | CA | 2E | E4 |       | JZ   | LOOP1        | BRANCH IF LAST, ELSE CONTINUE |

| E422 | 3C |    |    |       | INR  | $\mathbf{A}$ |                               |

| E423 | 32 | 02 | E0 |       | STA  | DIGIT        | INCREMENT TO NEXT DIGIT       |

| E426 | 23 |    |    |       | INX  | H            |                               |

| E427 | 22 | 00 | E0 | LOOP2 | SHLD | POINT        | POINT POINTS TO NEXT BCD WORD |

| E42A | E1 |    |    | •     | POP  | Н            |                               |

| E42B | FI |    |    |       | POP  | PSW          |                               |

| E42C | FB |    |    |       | E1   |              | ENABLE INTERRUPTS             |

| E42D | C9 |    |    |       | RET  |              |                               |

| E42E | 3E | 00 |    | LOOPI | MVI  | A,0          |                               |

| E430 | 32 | 02 | E0 |       | STA  | DIGIT        | RE-INITIALIZE DIGIT           |

| E433 | 21 | 03 | E0 |       | LXI  | H,0E003H     | RE-INITIALIZE POINT           |

| E436 | C3 | 27 | E4 |       | JMP  | LOOP2        |                               |

|      |    |    |    |       |      |              |                               |

Figure 17b. 8080A Interface to Refresh Controller Shown in Figure 15

# **CODED DATA CONTROLLER**

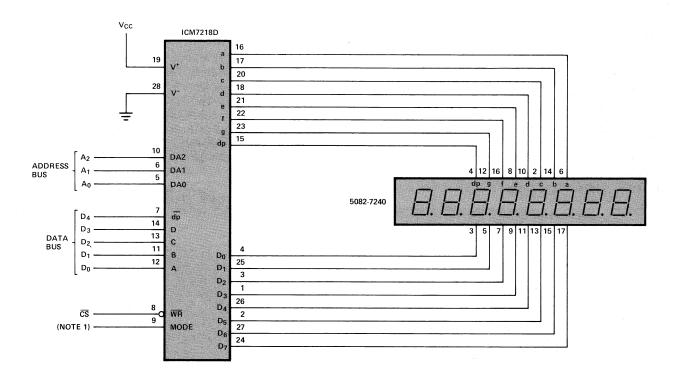

Figure 18 shows a Coded Data Controller designed for an eight character monolithic seven segment display. The circuit uses the Intersil ICM7218D to provide BCD data storage and display multiplexing. The ICM7218D is designed to drive common cathode LED displays at 10 mA IPEAK/segment (minimum) on a 12% duty cycle.

The circuit illustrated in Figure 18 uses the ICM7218D to drive an eight digit 5082-7240 monolithic LED display. The common anode version (ICM7218C) is rated at 20 mA IPEAK/segment (minimum). If higher drive currents are needed and a four digit display is acceptable, the eight

digit lines on the ICM7218D can be paralleled to drive four digits at twice the minimum current. The microprocessor interfaces to the ICM7218D through five Data Inputs (BCD and  $\overline{dp}$ ), three digit address lines (DA0, DA1, and DA2), a MODE input, and a  $\overline{WRITE}$  input. Data can be written in to the eight memory locations in the static memory of the ICM7218D via a three bit binary code on the digit address inputs. When the digit address lines are valid, a negative going  $\overline{WRITE}$  pulse clocks the BCD and dp data into the RAM. This method of memory addressing allows the user to update the display information only where it is necessary.

(NOTE 1) MODE IS A TRISTATE INPUT SUCH THAT WHEN MODE = HIGH, THE 7218 PROVIDES HEXIDECIMAL DECODING; WHEN MODE = FLOATING, THE 7218 PROVIDES CODE B DECODING; AND WHEN MODE = LOW, THE 7218 BLANKS THE DISPLAY.

Figure 18. Coded Data Controller

### **DECODED DATA CONTROLLER**

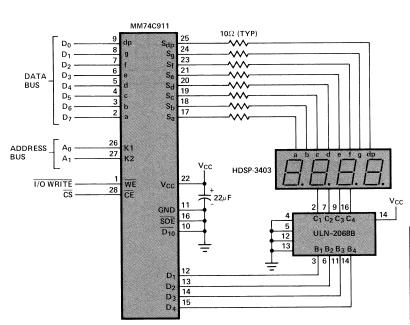

Figure 19 shows a Decoded Data Controller designed for use with 20.3mm (0.8 inch) seven segment displays. The circuit utilizes the National MM74C911 to directly drive four of the large seven segment displays. The MM74C911 is used to provide segment data storage and display multiplexing. The MM74C911 is designed to drive common cathode displays at 100 mA IPEAK/segment on a 25% duty cycle. The circuit illustrated in Figure 17 uses the MM74C911 to drive four HDSP-3403 20.3 mm (0.8 inch) standard red common cathode displays.

The microprocessor interfaces to the MM74C911 through eight data lines (a, b, c, d, e, f, g, dp), two address inputs  $K_1$  and  $K_2$ ,  $\overline{CHIPENABLE}$ , and  $\overline{WRITEENABLE}$ . The desired segment data is written into the register selected by the address information when  $\overline{CE}$  and  $\overline{WE}$  are low. This data is latched when either  $\overline{CE}$  or  $\overline{WE}$  return high. Data hold time is not required.

An internal oscillator sequentially presents the stored data to the output drivers which directly drive the LED display. The drivers are active when, the control pin labelled SEGMENT OUTPUT ENABLE (SOE) is low, and are tri-stated when SOE is high. This feature allows duty cycle brightness control for varying ambient light conditions. Also, SOE can be used to disable the output drivers for power conservation. The digit outputs directly drive the base of the digit transistor when the control pin labelled DIGIT INPUT OUTPUT (DIO) is low.

#### INTENSITY MATCHING

All Hewlett-Packard seven segment displays are tested for luminous intensity to ensure that data sheet values are

met. All displays which can be end stacked are categorized according to their intensity levels. The eye can detect roughly a 2:1 change in luminous intensity and, therefore, this is the criterion for intensity categories. This categorization allows end stacking of the displays, thereby providing a panel with a pleasing, uniform appearance.

The large seven segment displays are individually tested and categorized for luminous intensity. The intensity category is designated by a single or double letter located on the right hand side of the package. When end stacking, it is preferable that the user choose devices from a single category to provide uniform intensity across the display panel.

The monolithic seven segment display clusters are inherently intensity matched digit to digit in one display package. The immersion type monolithic displays which are designed for end stacking are categorized for intensity. The category is designated by a letter on the back side of the package. The user should choose devices from a single category when end stacking the displays.

### **COLOR MATCHING**

Color uniformity of the large seven segment displays is an important consideration. The standard red and high efficiency red displays have inherent color uniformity and need not be categorized. However, the eye is more sensitive to color differences in the yellow and green regions. Therefore, displays of these color types are categorized by dominant wavelength. This category is denoted by a number on the right hand side of the package. The user should choose units from a single category to achieve a display panel with optimal color uniformity.

|    | INPUT CONTROL |      |    |                 |  |  |  |  |  |  |  |

|----|---------------|------|----|-----------------|--|--|--|--|--|--|--|

| CE |               | RESS | WE | OPERATION       |  |  |  |  |  |  |  |

|    | K2            | К1   | 1  | 化多级合金 医多种性      |  |  |  |  |  |  |  |

| 0  | 0             | 0    | 0  | WRITE DIGIT 1   |  |  |  |  |  |  |  |

| 0  | 0             | 0    | 1  | LATCH DIGIT 1   |  |  |  |  |  |  |  |

| 0  | 0             | 1    | 0  | WRITE DIGIT 2   |  |  |  |  |  |  |  |

| 0  | 0             | 1    | 1  | LATCH DIGIT 2   |  |  |  |  |  |  |  |

| 0  | 1             | 0    | 0  | WRITE DIGIT 3   |  |  |  |  |  |  |  |

| 0  | 1             | 0    | 1  | LATCH DIGIT 3   |  |  |  |  |  |  |  |

| 0  | 1             | 1    | 0  | WRITE DIGIT 4   |  |  |  |  |  |  |  |

| 0  | 1             | 1    | 1  | LATCH DIGIT 4   |  |  |  |  |  |  |  |

| 1  | x             | x    | x  | DISABLE WRITING |  |  |  |  |  |  |  |

X = DON'T CARE

| DIO | SOE |    | DIGIT | LINES | OPERATION |                   |

|-----|-----|----|-------|-------|-----------|-------------------|

| טוט | SUE | D4 | D3    | D2    | D1        | OFERATION         |

| 0   | 0   | R  | R     | R     | R         | REFRESH DISPLAY   |

| 0   | 1   | R  | R     | R     | R         | DISABLE SEGMENTS  |

| 1   | 0   | 0  | 0     | 0     | 0         | DIGITS ARE INPUTS |

| 1   | 0   | 0  | 0     | 0     | 1         | DISPLAY DIGIT 1   |

| 1   | 0   | 0  | 0     | 1     | 0.        | DISPLAY DIGIT 2   |

| 1   | 0   | 0  | 1     | 0     | 0         | DISPLAY DIGIT 3   |

| 1   | 0   | 1  | 0     | 0     | 0         | DISPLAY DIGIT 4   |

| 1   | 1   | 0  | 0     | 0     | 0         | POWER SAVER MODE  |

R = REFRESH (DIGIT LINES SEQUENCIALLY PULSED)

Figure 19. Decoded Data Controller

# **SUNLIGHT VIEWABILITY**

The rapid growth of sophisticated electronic systems for use in avionic, automotive, machine, and military equipment has created the need for an electronic information display that is viewable in bright sunlight. By combining the newest LED product design technology and the most recent techniques for contrast enhancement, Hewlett-Packard can now provide the display system designer with devices that are useable in direct 107,000 lumens per square meter (10,000 foot candle) sunlight.

The HDSP-3530/-3730/-4030/-4130 series of large seven segment displays optimize the following parameters that contribute to the readability of the LED display in bright sunlight:

- a. LED Color

- b. Luminance Contrast

- c. Chrominance Contrast (color difference)

- d. Front Surface Reflections

These sunlight viewable display devices are assembled with Gallium Arsenide Phosphide (GaAsP) LED chips on a Gallium Phosphide (GaP) substrate. These materials produce the needed light output when driven with peak currents up to 120 mA. High current LED chips are used to allow high peak and average current in the display. The high efficiency red and yellow displays provide the most light output for a given input current and can easily be made visible in bright sunlight. The package configuration uses a neutral gray body and untinted segments to allow the display system designer to achieve readability by obtaining an optimum combination of both luminous and chrominance contrast. When placed behind a 20% to 25% neutral density gray filter, the illuminated segments provide a distinctly visible chrominance contrast with respect to the gray package.

# **MOUNTING CONSIDERATIONS**

The large segment display devices are constructed utilizing a lead frame in a standard DIP package. All 7.6mm (0.3 inch) and 10.9mm (0.43 inch) displays are manufactured with leads on 2.54mm (0.10 inch) centers with a row-to-row spacing of 7.6mm (0.3 inch). The 20.3mm (0.8 inch) displays are also on 2.54mm (0.10 inch) centers but the row-to-row spacing is 15.2mm (0.6 inch). The 14.1mm (0.56 inch) displays are on 2.54mm (0.10 inch) centers with row-to-row spacing of 15.2mm (0.6 inch). However, the leads are aligned along the top and bottom of the package rather than down the sides. Both the 14.1mm (0.56 inch) and 20.3mm (0.8 inch) displays can be socketed using a standard 24 pin IC socket or strip sockets. All large seven segment devices are end stackable and are designed for PC board mounting and wave soldering.

If the large segment devices are to be wave soldered, Sn60 or Sn63 solder is recommended. The solder wave is

recommended to be at 245° C with a dwell time of 1-1/2 to 2 seconds. The 20.3mm (0.8 inch) displays have a small tab at each corner to establish a 1mm (0.040 inch) seating plane above the printed circuit board. The other large seven segment displays have a shoulder on the lead frame to achieve a similar seating plane above the printed circuit board.

The non-immersion type monolithic displays may be mounted either by use of pins which may be soldered into the plated holes at the connector edge of the PC board or by insertion into a standard PC board connector (Table IV). The devices may be soldered for up to three seconds per tab at a maximum soldering temperature of 230°C. Heat should be applied only to the edge connector tab areas of the PC board. Heating other areas of the board to temperatures in excess of 85°C can result in permanent damage to the lens. It is recommended that a rosin core wire solder or a low temperature deactivating flux and solid wire be used in soldering operations.

The immersion type monolithic displays are designed for insertion into 12 or 14 pin DIP sockets or soldering into PC boards. All of these type of displays are manufactured on 2.54mm (0.100 inch) centers with a row-to-row spacing of 7.6mm (0.300 inch). If the displays are to be soldered into a PC board, the solder temperature must be kept at or below 245°C, 1/16 inch below the seating plane, for a maximum of five seconds. The shoulders of the lead frame pins are intentionally raised above the bottom of the package so that the display can be mounted at an angle to the PC board. Mounting angles up to 20° are often necessary in hand held or desk top applications and are easily attainable with immersion type monolithic displays. Refer to Application Note 937 for further instructions concerning installation of these devices.

LED displays, as well as all electronic components, operate more reliably at lower temperatures. Thermal considerations are important, and any method of cooling or heat sinking the displays will result in more reliable operation. Under no conditions should the absolute maximum temperature ratings be exceeded.

To optimize device optical performance, specially developed plastics are used in all display products. These plastics restrict the solvents that may be used for cleaning. Tests have demonstrated that the only fluorocarbon cleaner that is compatible with plastic LED devices is trichloro-fluoroethane (F113). This cleaner is sold commercially under the trade names Freon, Genesolv D, and Arkalone. Water can be used to clean both large seven segment displays and the immersion lens type monolithic displays. Water can also be used for hand cleaning the non-immersion type monolithic seven segment displays if care is taken to prevent water from collecting under the lens.

| Part<br>Number | Vendor*                    | Output<br>Structure    | Output<br>Current | Output<br>Active<br>State | Features                                                    |

|----------------|----------------------------|------------------------|-------------------|---------------------------|-------------------------------------------------------------|

| 74LS47         | TI, Fairchild,<br>National | Open Collector         | 24 mA             | Low                       | Auto Zero-Blanking, Lamp Test, 0-9                          |

| 74LS48         | TI, Fairchild,<br>National | 2K Pull-Up             | 6 mA              | High                      | Auto Zero-Blanking, Lamp Test, 0-9                          |

| 74LS49         | TI, National               | Open Collector         | 8 mA              | High                      | Auto Zero-Blanking, Lamp Test, 0-9                          |

| 8T04           | Signetics                  | Open Collector         | 40 mA             | Low                       | Auto Zero-Blanking, Lamp Test, 0-9                          |

| 8T06           | Signetics                  | Open Collector         | 40 mA             | High                      | Auto Zero-Blanking, Lamp Test, 0-9                          |

| 9368           | Fairchild                  | Open Emitter           | -19 mA            | High                      | Constant Current, Latch, Auto Zero-Blanking<br>0-9, A-F     |

| 9370           | Fairchild                  | Open Collector         | 40 mA             | Low                       | Latch, Auto Zero-Blanking, 0-9, A-F                         |

| 9384           | Fairchild                  | Current Mirror         | 15 mA             | Low                       | Constant Current, Latch, Auto Zero-Blanking<br>0-9, E,H,C,D |

| DS8669         | National                   | Open Collector         | 25 mA             | Low                       | 2 Digit (14 Outputs), 0-9, C,A,P,E,H,J,L,F,-                |

| MC14511        | Motorola                   | NPN Bipolar<br>Emitter | -25 mA            | High                      | Latch, Lamp Test, Blanking Input, 0-9                       |

| MC14547        | Motorola                   | NPN Bipolar<br>Emitter | -65 mA            | High                      | Latch, Blanking Input, 0-9                                  |

<sup>\*</sup>This is a partial list of vendors. Other suppliers for the same part may exist.

**TABLE II. Display Drivers**

|      | Part<br>Number        | Vendor*                                 | Number<br>of<br>Drivers | Input<br>Compatibility | Output<br>Current<br>(mA) | Features                                    |

|------|-----------------------|-----------------------------------------|-------------------------|------------------------|---------------------------|---------------------------------------------|

|      | DS8859                | National                                | 6                       | ŤŤL                    | 0-40 (Max)                | Programmable Constant Current               |

|      | DS8867                | National                                | 8                       | 7V MOS                 | -14 (Typ)                 | Constant Current                            |

|      | DS8877                | National                                | 6                       | MOS, TTL               | 50 (Typ)                  | Low Current Version of 75492                |

|      | DS8874/76/79          | National                                | 9                       | 9V MOS                 | 50 (Min)                  | Serial Input, Low Battery Indicate          |

| -210 | ULN-2031/33           | Sprague                                 | 7                       | TTL, 5V-15V CMOS       | ±80 (Max)                 | NPN or PNP Darlington Pair                  |

| 40 - | 75497/498             | TI                                      | 7                       | MOS, TTL               | 125 (Max)                 |                                             |

|      | 75492                 | TI, Fairchild,<br>Motorola,<br>National | 6                       | 9 MOS                  | 250 (Max)                 | Darlington Pair                             |

|      | DS8870                | National                                | 6                       | 9V MOS                 | 350 (Max)                 |                                             |

|      | DS8863/8963           | National                                | 8                       | 9V MOS                 | 500 (Max)                 |                                             |

|      | ULN-2003A<br>(MC1413) | Sprague, TI<br>Motorola                 | 34 may 1 m 1 m          | TTL, 5V CMOS           | 500 (Max)                 | 2.7 kΩ Series Resistance to Darlington Pair |

|      | ULN-2981A             | Sprague                                 | 8                       | TTL, 5V CMOS           | -500 (Max)                |                                             |

|      | ULN-2068B             | Sprague                                 | 4                       | TTL, 5V CMOS           | 1500 (Max)                | Predriver Stage to Darlington Pai           |

| Part<br>Number | Vendor*       | Number<br>of<br>Drivers | Input<br>Compatibility | Output<br>Current<br>(mA) | Features                         |

|----------------|---------------|-------------------------|------------------------|---------------------------|----------------------------------|

| 74LS259        | TI, Signetics | 8                       | TTL                    | 8 (Max)                   | Active High, Four Mode Operation |

| DS8665         | National      | 14                      | 9V MOS                 | -20 (Max)                 | Active Low, Oscillator Output    |

| NE590          | Signetics     | 8                       | TTL                    | 250 (Max)                 | Active Low, Four Mode Operation  |

<sup>\*</sup>This is a partial list of vendors. Other suppliers for the same part may exist.

# **TABLE III. Multifunction Display Drivers**

# COUNTERS

| Part Number          | Vendor                                                                                                                                                                                      | Function                                                                                                                                        | Drive Conditions                                                                                                                                          |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MM74C925/6/7/8 Natio |                                                                                                                                                                                             | CMOS counter with internal output latch and self-contained internal oscillator and scanning circuitry                                           | 4 Digit Common Cathode<br>40 mA pk (typ) 1 of 4 D.F.                                                                                                      |  |  |  |

| MK50395-9            | MOSTEK                                                                                                                                                                                      | Six decade counter/display decoder;<br>look ahead carry or borrow, loadable<br>counter                                                          | 6 Digit Common Anode segment and digit drivers required                                                                                                   |  |  |  |

| MK5002/517           | MOSTEK                                                                                                                                                                                      | Four decade counter, latch, decoder with leading zero blanking                                                                                  | 4 Digit Common Anode or Common Cathode segment and digit drivers required                                                                                 |  |  |  |

| ICM7217<br>ICM7227   | Intersil                                                                                                                                                                                    | CMOS up/down counter; presettable start/count and compare register; for hard-wired microprocessor control applications; cascadable              | 4 Digit Common Cathode (A,C)<br>12.5 mA pk (typ), 10 mA pk (min) 1 of 4 D.F.<br>Four Digit Common Anode (B)<br>40 mA pk (typ), 25 mA pk (min) 1 of 4 D.F. |  |  |  |

| ICM7208              | Intersil                                                                                                                                                                                    | Seven decade counter with scanning circuitry, display blanking, reset                                                                           | 7 Digit Common Cathode<br>15 mA pk (typ) 1 of 8 D.F.                                                                                                      |  |  |  |

| ICM7225              | Intersil                                                                                                                                                                                    | High speed (25 MHz typ) counter/<br>decoder/driver                                                                                              | 4-1/2 Digit Common Anode<br>8 mA dc (typ), 5 mA dc (min)                                                                                                  |  |  |  |

| ICM7216<br>ICM7226   | 6 Intersil Universal Counter that measures frequency, period, frequency ratio, time interval, units  8 Digit Common Anode (A/C) 35 mA pk (typ), 25 mA pk (min) 8 Digit Common Cathode (B/D) |                                                                                                                                                 | 35 mA pk (typ), 25 mA pk (min) 1 of 8 D.F.                                                                                                                |  |  |  |

| ZN1040E              | Ferranti<br>Packard                                                                                                                                                                         | Universal Up/Down Synchronous<br>Counter, with separate memory latches,<br>look ahead or borrow, internal<br>oscillator, and scanning circuitry | 4 Digit Common Anode or Common<br>Cathode<br>80 mA pk (typ), 50 mA pk (min) 1 of 4 D.F.                                                                   |  |  |  |

# **DISPLAY CONTROLLERS**