### **APPLICATION NOTE 967**

# A Low Noise 4 GHz Transistor Amplifier Using the HXTR-6101 Silicon Bipolar Transistor

#### CONTENTS

I. INTRODUCTION

II. HPAC-70 GT PACKAGE

III. DESIGN DATA

IV. INPUT MATCHING NETWORK

V. OUTPUT MATCHING NETWORK

VI. COMPUTER SIMULATION

VII. PERFORMANCE

VIII. CONSTRUCTION

APPENDIX A – SCATTERING PARAMETERS VS. COLLECTOR CURRENT AT 4 GHz

APPENDIX B - NOISE PARAMETERS VS. COLLECTOR CURRENT AT 4 GHz

APPENDIX C - AN ACTIVE D.C. BIASING NETWORK

APPENDIX D — PARAMETERS AT VARIOUS BIAS CONDITIONS AT 4 GHz

#### SYMBOLS

|Sii| - Magnitude of Sii where i, j equals 1,2

/Sij - Angle of Sij where i, j equals 1,2

|S<sub>ij</sub>|<sup>2</sup> - Power Ratio of S<sub>ij</sub> where i, j equals 1,2

S<sub>11</sub> - Input Reflection Coefficient

S<sub>12</sub> - Reverse Transmission Gain

S21 - Forward Transmission Gain

S22 - Output Reflection Coefficient

S'22 – Output Reflection Coefficient with the source reflection coefficient being Γ<sub>Ω</sub>

Q(S'22) - Unloaded Quality Factor of S'22

Z'22 - Equivalent Impedance of S'22

K - Stability Factor

Ga(max)- Maximum Available Power Gain

Γ<sub>MS</sub> - Source Reflection Coefficient for G<sub>a(max)</sub>

Γ<sub>ML</sub> - Load Reflection Coefficient for G<sub>a(max)</sub>

F<sub>MIN</sub> - Minimum Noise Figure

M<sub>MIN</sub> - Minimum Noise Measure

Ga - Associated Gain at FMIN

Rn - Equivalent Noise Resistance

ZNF - Equivalent Impedance of Γο

Γ<sub>O</sub> – Optimum Source Reflection Coefficient for F<sub>MIN</sub>

Γ<sub>L</sub> - Load Reflection Coefficient for F<sub>MIN</sub>

P<sub>1dB</sub> - Power Output at 1 dB gain compression

Ptune - Input Power Level when tuned for maximum

power output

η<sub>C</sub> - Collector RF to DC Power Efficiency at 1dB

gain compression

ΓPS - Source Reflection Coefficient for P<sub>1dB</sub>

Γ<sub>PL</sub> - Load Reflection Coefficient for P<sub>1dB</sub>

#### INTRODUCTION

A significant improvement in the producibility, consistency, noise figure and associated gain of low noise microwave bipolar transistors has been realized with Hewlett-Packard's development of a fully ion implanted device with sub-micron emitter widths. State-of-the-art noise performance is obtained with the chip mounted in the HPAC-70GT package (HXTR-6101).

The purpose of this application note is to describe in detail the design of a single-stage state-of-the-art low noise amplifier at 4 GHz. The design and construction of both the input and output matching networks of a microstrip amplifier will be described. The amplifier's 4 GHz performance is excellent, with a noise figure of 2.6 dB, an associated gain of 10.8 dB and a 4.5 dBm power output at 1 dB gain compression. The

third order intercept point is +17 dBm with an output VSWR of 1.29. An active biasing network is used for good temperature performance. Noise Figure and gain on the amplifier is presented over the temperature range of -55°C to +110°C. Although the design of the amplifier was for 4.0 GHz, the performance over the 3.7 to 4.2 GHz telecommunication band is very good.

The initial design goals are:

- Amplifier noise figure less than 3.0 dB

- Associated gain greater than 8 dB

- Noise measure less than 3.4 dB

- Output VSWR of less than 1.5:1

#### HPAC-70GT PACKAGE

The HXTR-6101 is supplied in the HPAC-70GT, a rugged co-fired alumina/kovar hermetic package. The unique feature of this patented package is that the closest external emitter connection on the package is the kovar top cap. The reduction in emitter inductance is a factor of two improvements over the HPAC-100. The typical value of emitter inductance to the kovar top cap is 0.09nH. This reduced inductance increases the high frequency performance of the packaged device.

The HXTR-6101 worst case thermal impedance is 250° C/W with the emitter top cap connected to a large heat sink. Use is made of the emitter top cap for both thermal and R.F. grounding.

#### **DESIGN DATA**

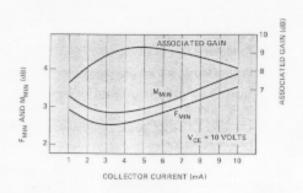

Plotted in Figure 1 is the typical noise figure, noise measure \* and associated gain of the HXTR-6101 product as a function of collector current at 4 GHz.

From Figure 1, it can be seen that the minimum noise measure of the device is obtained at a collector current of 3 to 4

Figure 1. Typical Noise Figure and Associated Gain vs. Collector Current.

\*The system noise figure of an infinite cascaded chain of identical amplifier stages. For further explanation, see Hewlett-Packard application bulletin #9.

$$M_{MIN} = 10 \log_{10} \left[ 1 + \frac{F_{MIN} - 1}{1 - \frac{1}{Ga}} \right]$$

mA. However, the associated gain at noise figure is higher at 4mA, therefore a bias point of  $V_{CE}$  = 10 volts and  $I_{C}$  = 4 mA is chosen for low noise measure operation. At these bias conditions, the scattering, gain<sup>(1)</sup> and noise<sup>(2)</sup> parameters for the particular device used in this amplifier are:

| Scattering Parameters        | Gain Parameters                   |

|------------------------------|-----------------------------------|

| $S_{11} = 0.552/169^{\circ}$ | k = 1.012                         |

| S <sub>12</sub> = 0.049/23°  | $G_{a(max)} = 14.7 dB$            |

| S <sub>21</sub> = 1.681/26°  | $\Gamma_{MS} = .941/-154^{\circ}$ |

| $S_{22} = 0.839/-67^{\circ}$ | Γ <sub>M1</sub> = 979/70°         |

#### Noise Parameters

$F_{MIN} = 2.5 \text{ dB}$   $\Gamma_{O} = .475/166^{\circ}$  $R_{D} = 3.5 \text{ ohms}$

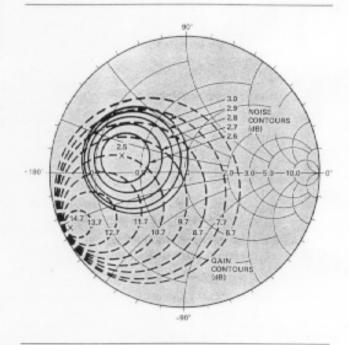

Using the Scattering and Noise Parameters above, the available power gain and noise contours are plotted in Figure 2. The contours are mapped onto the source impedance plane<sup>[2]</sup>

Figure 2. Noise and Gain Contours

Taking a closer look at the Noise Contours, it is seen that the optimum source reflection coefficient ( $\Gamma_{\rm O}$ ) for minimum noise figure ( $F_{\rm MIN}$ ) is not very sensitive to matching error. The diameter of the first noise contour corresponds to a change in reflection coefficient magnitude of .37 with a noise figure increase of 0.1dB. This characteristic of the HXTR-6101 is very advantageous to circuit designers tryingto match for minimum noise figure. From the two sets of contours, it appears that the associated gain at minimum noise figure will be approximately 11 dB with the output seeing a conjugate match.

Since the design goal is to construct a low noise amplifier, the optimum noise measure bias condition is selected. There is also an optimum bias condition for maximum gain and another for output power. Even at the optimum noise mea-

sure bias there are trade-offs between noise figure, gain and power output due to source and load impedance.

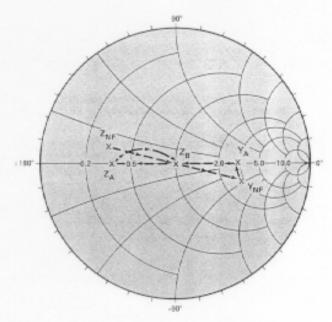

At the optimum noise measure bias of  $V_{CE} = 10$  volts and  $I_{C} = 4$ mA, the source and load reflection coefficients for lowest noise figure, maximum gain and greatest power are tabulated and plotted in Figure 3. Figure 3 is plotted for the particular device used in this amplifier design. The source and load reflection coefficients are mapped onto the source or load impedance plane.

Figure 3. Matching Tradeoffs

#### INPUT MATCHING NETWORK

The main purpose of the input matching network is to provide the optimum source impedance for minimum noise figure. The basic design philosophy in realizing this network is:

- Convert the optimum source reflection coefficient (Γ<sub>O</sub>) to impedance.

- From this impedance determine the equivalent admittance.

- The susceptance component is realized with a short circuited eighth-wave (<sup>λ</sup>/<sub>α</sub>) length stub.

- The conductance component is realized with a quarterwave (<sup>λ</sup>/<sub>λ</sub>) length impedance transformer.

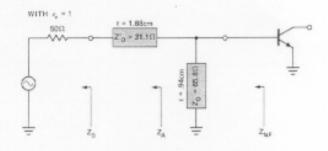

The realization and Smith Chart mapping for this input matching network is described below and shown in Figure 4.

1) The impedance  $Z_{NF}$ , corresponding to  $\Gamma_O = .475/166^{\circ}$  is:

$$Z_{NF} = \frac{(1 - |\Gamma_{O}|^{2}) 50}{1 + |\Gamma_{O}|^{2} - 2 |\Gamma_{O}| \cos \sqrt{\Gamma_{O}}} + \frac{j (2 |\Gamma_{O}| \sin \sqrt{\Gamma_{O}}) 50}{1 + |\Gamma_{O}|^{2} - 2 |\Gamma_{O}| \cos \sqrt{\Gamma_{O}}}$$

$$Z_{NF} = 18.0 + j 5.35$$

2)

$$Y_{NF} = \frac{1}{Z_{NF}} = 0.0510 - j 0.0152$$

A short circuited stub less than a quarter-wave length long looks like a shunt inductor of impedance Z = jZ<sub>Q</sub> tan βℓ. Hence a short circuited stub that is an eighth-wave length long looks like a shunt inductor of impedance  $jZ_O$  where  $Z_O$  is the characteristic impedance of the stub. Hence

$$Z_0 = \frac{1}{.0152} = 65.8 \text{ ohms.}$$

Since the driving source impedance is 50Ω, a quarter-wave transformer of characteristic impedance:

$$Z'_{O} = \sqrt{(50)(19.6)} = 31.31\Omega$$

completes the input matching network.

Figure 4. Input Matching Network

#### OUTPUT MATCHING NETWORK

With one of the design goals being an output VSWR of less than 1.5:1, the output matching network is designed to provide a conjugate match with the source impedance,  $Z_{\rm NF}$ . The basic design procedure is:

- Calculate S'<sub>22</sub>, the output reflection coefficient with the source reflection coefficient being Γ<sub>O</sub>.

- Provide a conjugate match for the output with a load reflection coefficient equal to S'<sub>22</sub>\*. (Γ<sub>L</sub> = S'<sub>22</sub>\*)

- 3) The matching section could be realized with a shunt stub and a series transformer similar to the input network. However, in order to increase the tuning capabilities of the network, an extra section of matching is used.

The realization and Smith Chart mapping of this output network is described below and shown in Figure 5.

From the S-Parameters on the device, S'<sub>22</sub> can be calculated as follows:

$$S'_{22} = S_{22} + \frac{S_{21} S_{12} \Gamma_0}{1 - S_{11} \Gamma_0}$$

Now, providing a conjugate match to  $S_{22}$  for a good output VSWR, the load reflection coefficient ( $\Gamma_L$ ) should be:

$$\Gamma_{L} = .846/72^{\circ}$$

A problem with the output is the relatively high Q. This

can cause problems in supplying a conjugate load match

to obtain a good output VSWR because of sensitivity to

small dimensional changes. Calculating this output Q

gives us,

$$Q(S'_{22}) = 5.65$$

With this dominant Q, the calculated 3 dB bandwidth (B.W.) is:

$$100 \times \frac{B.W.}{f_0} = \frac{100}{Q(S'_{22})} = 18\%$$

This bandwidth equals 720 MHz with a center frequency (f<sub>0</sub>) of 4 GHz.

3) A 0.61 cm (2βl = 59°) equivalent air length of Z<sub>O</sub>=50Ω transmission line was added to the output to provide an output soldering area. The rotated output reflection coefficient is:

Γ<sub>1</sub> = .846/-131°

The corresponding impedance,  $Z_1$ , is

$$Z_1 = \frac{(1 - |\Gamma_1|^2)}{1 + |\Gamma_1|^2 - 2|\Gamma_1| \cos /\Gamma_1} + \frac{j \left(2 |\Gamma_1| |S_{in} /\Gamma_1\right)}{1 + |\Gamma_1|^2 - 2|\Gamma_1| \cos /\Gamma_1}$$

$$Z_1 = 5.03 - j 22.6$$

$$Y_1 = \frac{1}{Z_1} = 9.35 \times 10^{-3} + j.0422$$

4) A short circuited stub an eighth-wave length long looks like a shunt inductor of admittance, -j Y<sub>0</sub>. The purpose of this shunt stub is to tune out most of the susceptance component in the admittance Y<sub>1</sub>. A tuning section will be added to further match the output.

A convenient characteristic admittance,  $Y_0 = 0.0345$   $\Im$  is used for the shunt stub.

$$Y_2 = 9.35 \times 10^{-3} + j.0422 - j.0345 = 9.35 \times 10^{-3} + j.0077$$

$Z_2 = \frac{1}{Y_2} = 63.7 - j.52.5$

5) The next element is a transformer to obtain an admittance with real part matched to the 50 ohm load. This is accomplished with an 80 ohm line 1.35 cm long, ( $\epsilon_{\rm f}$ =1) ( $\beta \ell$  = 64.8°)

$$Z_3 = \frac{Z_0 \{Z_2 + j Z_0 \tan \beta \bar{x}\}}{\{Z_0 + j Z_2 \tan \beta \bar{x}\}}$$

$$Z_3 = 39.12 + j 21.1$$

$$Y_3 = \frac{1}{Z_3} = .02 - j.0107$$

6) An open stub is chosen to provide some tuning capability. An open circuited stub less than a quarter-wave length long looks like a shunt admittance Y = j Y<sub>0</sub> tan βℓ. An open circuited stub of characteristic admittance Y<sub>0</sub> = .039 ♂ and length 0.4 cm (ε<sub>f</sub> = 1) (βℓ = 19.2°) is added.

$$Y_4 = .02 - j.0107 + j.0136 = .02 + j.0029$$

$$Z_4 = \frac{1}{Y_A} = 50 - j 7.1$$

7) Now Z<sub>4</sub> is matched with a transformer with a characteristic impedance of 80  $\Omega$  and length of .19 cm ( $\epsilon_f$  = 1) ( $\beta\ell$  = 9.12°)

$$Z_5 = \frac{Z_0 (Z_4 + j Z_0 \tan \beta \hat{x})}{(Z_0 + j Z_4 \tan \beta \hat{x})} = 50 \Omega$$

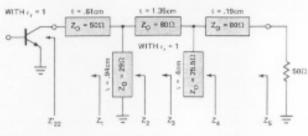

Figure 5. Output Matching Network

The output tuning section as described has the flexibility for tuning in four areas:

- · Adjusting the length of the series line

- Changing the width or characteristic impedance of the open circuited shunt stub

- · Modifying the length of the shunt stub

- · Varying the length of the final series line

This completes the design of the output matching network.

#### COMPUTER SIMULATION

With the S-Parameters for the particular device used, the input and output matching networks were modeled as simulated on a circuit analysis program. The results of this simulation yield the following results:

$S_{11} = .620/51.2^{\circ}$  Input VSWR = 4.26  $S_{21} = 11.04dB/-113.8^{\circ}$  or Gain = 11.04dB  $S_{12} = -19.67dB/-116.8^{\circ}$  Solution = -19.67dB  $S_{22} = .089^{\circ}/-87.3$  Output VSWR = 1.20\*

#### PERFORMANCE

An amplifier was constructed using the design derived above. A comparison of the computer simulation with measured amplifier performance at 4 GHz is shown below.

| Parameter     | Measured<br>Performance | Design<br>Goal | Computer<br>Simulation |

|---------------|-------------------------|----------------|------------------------|

| Gain          | 10.8 dB                 | 8.0 dB (MIN.)  | 11.0 dB                |

| Input VSWR    | 3.57                    |                | 4.26                   |

| Output VSWR   | 1.29                    | 1.50 (MAX.)    | 1.20                   |

| Isolation     | -24 dB                  |                | -19.7 dB               |

| Noise Figure  | 2.60 dB*                | 3.0 dB (MAX.)  | -                      |

| Noise Measure | 2.77 d8                 | 3.4 dB (MAX.)  | - 1                    |

<sup>\*</sup>Device Noise Figure is 2.5 dB

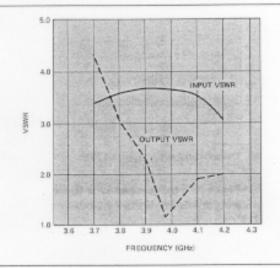

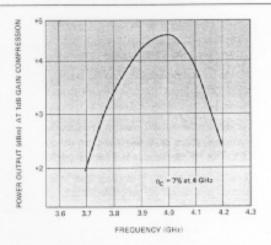

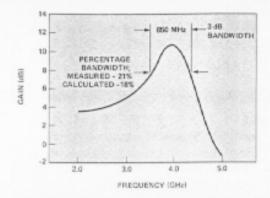

Although the design of the amplifier was for low noise performance at 4.0 GHz, the performance over the 3.7 to 4.2 GHz telecommunication band is very good.

Figures 6, 7 and 8 show the room temperature performance of the amplifier.

Phase Linearity - Phase linearity is ±5° over the entire 500 MHz band width.

Isolation - Isolation is better than -24 dB over the entire 3.7 to 4.2 GHz band.

AM to PM Conversion – With an output power level of – 13 dBm, the input power level is referenced. At this input reference level, the input power is varied ± 10dBm. Over the 3.7 to 4.2 GHz band, the AM to PM conversion is less than 0.13°/dB.

Third Order Intercepts – With two fundamental signals injected into the input at 3.95 and 4.05 GHz, the output power level for each fundamental signal is set at 0 d3m. The third order intermodulation products are both –34 d8 below the two fundamentals at the output. Therefore, the third order intercept point is + 17 d8m.

Spurious Outputs - With a 4 GHz, 0 dBm input signal injected into the amplifier, no spurious signals were detected above -60 dBm over the 2 to 6 GHz band.

Group Delay - The group delay over the entire 500 MHz bandwidth is less than .53 n sec.

Wideband gain performance is plotted in Figure 9.

Figure 6. Noise and Gain Performance.

Figure 7. Input - Output VSWR Performance.

Figure 8. Power Output Performance.

<sup>\*</sup>The output VSWR is not 1.00 because of round off error in design.

Figure 9, Wideband Gain Performance.

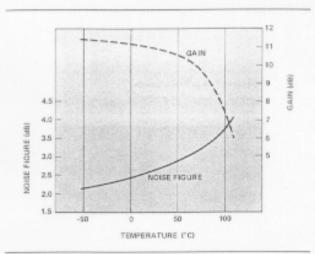

Figure 10. Temperature Performance at 4 GHz.

Plotted in Figure 10 is the gain and noise figure performance of the amplifier at 4 GHz over the temperature range of  $-55^{\circ}$  C to  $+110^{\circ}$  C.

#### CONSTRUCTION

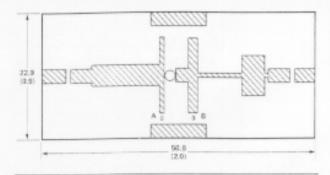

The board material is .031" RT/Duroid 120-061 (D5880), with 1 oz copper clad on two sides. The relative dielectric constant ( $\epsilon_r$ ) is 2.23. Duroid was chosen because of its low loss tangent. The thickness of .031" was chosen so the emitter top cap could be soldered to the RF ground, thereby taking advantage of the low emitter inductance.

To minimize transition interactions between the series transmission lines and shunt stubs, the shunt stubs were balanced along the series transmission lines.

Some tuning on the output matching network was required. The final realization of this circuit on duroid is shown in Figure 11. The RF board size is 2 inches by 0.9 inches.

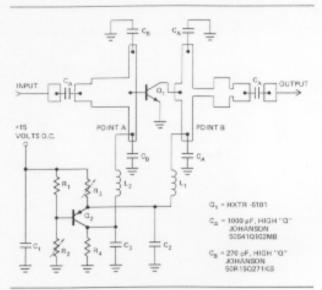

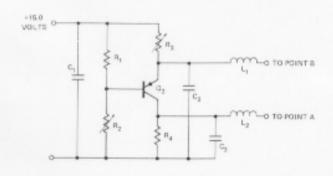

The active biasing network is described in Appendix C. A schematic of the complete amplifier and biasing circuit can be seen in Figure 12.

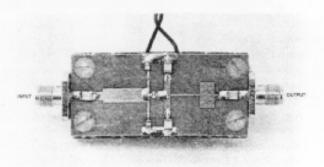

Pictures of the assembled amplifier can be seen in Figures 13 and 14. The amplifier draws 4.4mA from a 15 volt D.C. power supply.

Figure 11. R.F. Board Layout.

Figure 12. Complete Amplifier Schematic.

Figure 13. Amplifier - Top View.

Figure 14. Amplifier - Bottom View.

#### APPENDIX A SCATTERING PARAMETERS VERSUS COLLECTOR CURRENT AT 4 GHz.

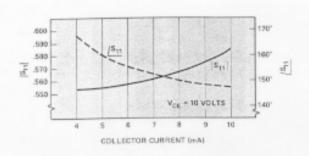

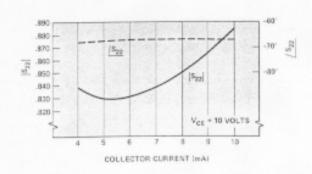

Figure A1. S<sub>11</sub> - Input Reflection Coefficient.

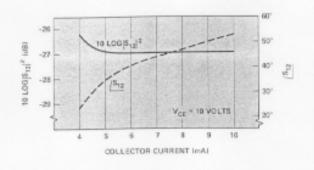

Figure A2. S<sub>12</sub> - Reverse Transmission Gain.

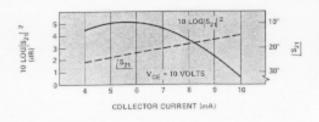

Figure A3. S21 - Forward Transmission Gain.

Figure A4. S22 - Output Reflection Coefficient.

#### APPENDIX B

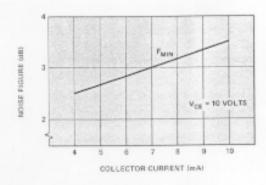

## NOISE PARAMETERS VERSUS COLLECTOR CURRENT AT 4 GHz.

Figure B1. FMIN - Minimum Noise Figure.

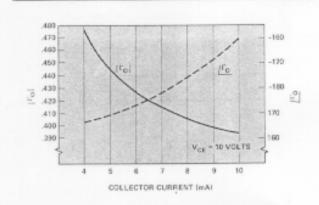

Figure B2. I'O - Optimum Source Reflection Coefficient for FMIN-

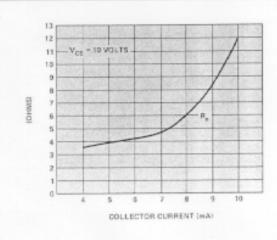

Figure B3. R<sub>n</sub> - Equivalent Noise Resistance.

#### APPENDIX C

#### AN ACTIVE D.C. BIASING NETWORK

The purpose of a bias circuit is to hold the quiescent point constant. A resistor network could be used with good results over a moderate temperature range. For this particular amplifier an active biasing network was used to maintain a relatively constant quiescent point over a temperature range of -55°C to +110°C. The noise figure and gain of the constructed amplifier was measured over this temperature range (Figure 10).

With a power supply voltage of +15 volts chosen for the amplifier, the active biasing network is shown below along with the components used:

Figure C1.

| Element        | Value                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------|

| R <sub>1</sub> | 100 KΩ,¼W                                                                                                               |

| R <sub>2</sub> | 200 KΩ, 1W, potentiometer                                                                                               |

| R <sub>3</sub> | 5 K $\Omega$ , 1W, potentiometer                                                                                        |

| R <sub>4</sub> | 2.61 KΩ, ¼W                                                                                                             |

| C <sub>1</sub> | .01µF, 100v, disc.                                                                                                      |

| C2             | .002µF, 250v, disc.                                                                                                     |

| C <sub>3</sub> | .01µF, 100v, disc.                                                                                                      |

| Lı             | 2 turns #36 enameled wire on .1" core (air)                                                                             |

| L <sub>2</sub> | 2 turns #36 enameled wire on .1" core (air)                                                                             |

| O <sub>2</sub> | $H_{FE} \ge 75$ , $f_T > 150$ MHz, $BV_{CEO} \ge 30V$ , $I_{C max} \le 50 mA$ , $P_D \le 300$ mW, PNP Silicon, Plastic. |

The quiescent point is adjusted by  $R_2$  and  $R_3$ ,  $R_2$  is adjusted to provide the proper  $V_{CE}$  voltage and  $R_3$  is adjusted to supply the correct collector current ( $I_C$ ).

Further explanation on this active biasing network may be found in Hewlett-Packard's Application Note 949-1, Page 5.

#### APPENDIX D

#### PARAMETERS AT VARIOUS BIAS CONDITIONS AT 4 GHz

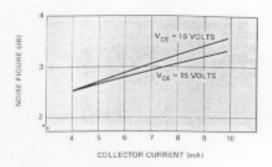

Figure D1. Noise Figure vs. Collector - Emitter Voltage.

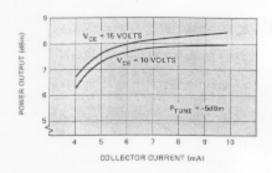

Figure D2. Power Output at 1 dB Gain Compression vs. Collector — Emitter Voltage.

#### REFERENCES

- Hewlett-Packard Application Note 95-1, "S-Parameter Techniques for faster, more accurate Network Design", September 1968, Page 12.

- Hewlett-Packard Application Note 154, "S-Parameter Design", April 1972, Pages 26 and 27.

Hewlett Packard assumes no responsibility for the use of any circuits described herein and makes no representations or womenties, express or implied, that each circuits are free from patent infringement.

For more information, call your local HP Sales Office or Emit (301) 948-6370 - Michwest (312) 677-0400 - South (404) 434-4000 - West (213) 877-1282. Or write Hawlest-Packard Components, 640 Page Mill Road, Palo Alto, Californio 94304. In Europe, Post Office Box 85, CH-1217, Meyrin 2, Geneve, Switzerland, In Japan, YHP, 1-59-1, Yoyogi, Shibuya-Ku, Tokyo, 151.